## Architettura interna della gamma migliorata

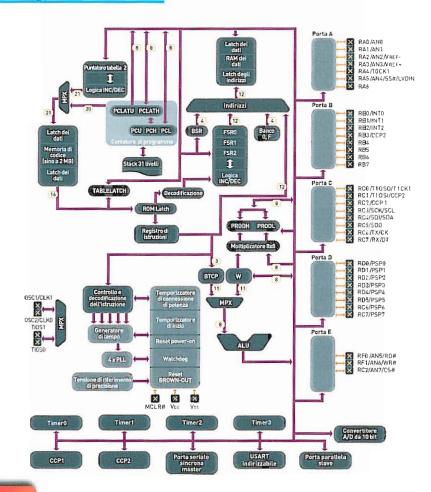

architettura dei PIC18CXXX è simile a quella dei PIC16F87X, però con più registri, più dispositivi e più capacità della memoria. La gamma migliorata dispone di un temporizzatore in più rispetto alla gamma media. Il Contatore di Programma ha una lunghezza maggiore, per indirizzare uno spazio di memoria maggiore: con 21 bit è capace di indirizzare 2 M indirizzi. Lo Stack possiede 31 livelli da 21 bit ognuno.

L'indirizzo che punta alla memoria dei dati è da 12 bit, quindi sarà possibile gestire fino a 4 KB. Dispone di un moltiplicatore rapido da 8 x 8 bit e unità per l'incremento e il decremento automatico degli indirizzi. Nello schema della figura è riportata l'architettura interna dei PIC18CXXX con contenitore da 40 pin e 5 porte di I/O.

## La memoria di programma

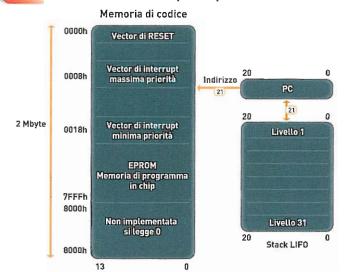

Fa riferimento al Contatore di Programma da 21 bit e può arrivare a una capacità massima di 2 M indirizzi. Come si vede nella figura, il vector di Reset occupa l'indirizzo 0000H, quelli di interrupt gli indirizzi da 0008H a 0018H. I 31 livelli dello Stack si indirizzano con un puntatore da 5 bit che si pone automaticamente a 0 quando c'è un Reset. Esistono, inoltre, flag di "Stack pieno" e "Overflow".

Schema generale dell'architettura interna dei PIC18CXXX con 40 pin e 5 porte di I/O.

Organiz<mark>zazione</mark> general<mark>e della</mark> memoria di programma nei PIC18CXXX.

## Altri modelli di PIC

Per quanto riguarda il repertorio delle istruzioni troviamo PUSH e POP, che permettono di inserire e prendere i valori dallo Stack tramite programma. Dato che la memoria di programma si indirizza con byte e ogni istruzione è composta da 2 byte. è importante che l'indirizzo di inizio di ogni istruzione sia pari, cioè, che il bit meno significativo dell'indirizzo sia 0. Il valore del PC posiziona i suoi 21 bit su tre registri specifici: gli 8 bit meno significativi in PCL, gli 8 bit successivi in PCH, e i 5 più significativi nel registro PCU.

## La memoria dei dati

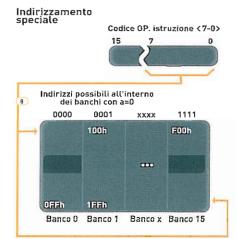

La memoria si gestisce con indirizzi da 12 bit, potendo arrivare a una dimensione massima di 4 K indirizzi da 8 bit. La mappa della memoria si divide in 16 banchi da 256 byte ognuno. Per indirizzare una cella di questa memoria si utilizzano due campi, il primo da 4 bit seleziona il banco ed è configurato con i 4 bit meno significativi del registro

Indirizzamento diretto

BSR <3-0>

X X X X

Indirizza all'interno

del banco

0000 0001 xxxx 1111

000h 100h F00h

OFFh 1FFh

Banco 0 Banco 1 Banco x Banco 15

Selezione del banco

Indirizzamento diretto alla memoria dei dati. Il banco lo selezionano i 4 bit del registro BSR e gli indirizzi degli 8 bit meno significativi del formato dell'istruzione. BSR (Registro di Selezione di Banco). L'altro campo ha 8 bit che sono inseriti nel formato stesso dell'istruzione, come possiamo vedere nella figura.

Nell'indirizzamento diretto l'istruzione specifica l'indirizzo dell'operando nella memoria. Il formato del codice binario dell'istruzione, INS <15:0>. è ripartito nei seguenti campi. I 6 bit meno significativi, INS <15:10>, contengono il codice OP dell'istruzione; il bit INS <9> indica la destinazione del risultato, quindi se vale 0 la destinazione è W e se vale 1 è il registro sorgente f. Il bit INS <8> sí chiama "a" e seleziona il tipo di accesso alla memoria dei dati. Se a = 1 si accede al banco determinato dai 4 bit meno significativi del registro BSR. Se a = 0 si utilizza l'indirizzamento speciale "Accesso a Banco", il cui comportamento è riportato graficamente nella figura. Nella figura in basso possiamo vedere la codificazione in binario dell'istruzione "addwf f, d, a" per il caso specifico "addwf 004h, 0, 1". L'accesso all'operando si realizzerà al banco della memoria dei dati, determinato dai bit BSR <3:0>, l'indirizzo sarà lo 004 h e il registro di destinazione sarà W. Per poter gestire con comodità la memoria dei dati sono state progettate alcune istruzioni formate da due word da 16 bit. La prima destina i 4 bit più significativi al codice OP

Quando il bit a = 0 (INS <8>) si accede solamente con gli 8 bit meno significativi del codice (INS <7:0>). I 256 byte accessibili sono formati dai primi 128 byte del Banco 0 e dagli ultimi 128 byte del Banco 15.

e i 12 rimanenti si utilizzano per indirizzare lo spazio da 4 K dove risiede l'operando sorgente.

La seconda word ha sempre i suoi 4 bit più significativi a valore 1 e i 12 rimanenti puntano all'operando di destinazione. Ad esempio l'istruzione "movff s.d" trasferisce il contenuto dell'indirizzo della memoria dei dati s alla posizione d. La seconda word delle quattro istruzioni speciali che possiedono un codice a due word, inizia sempre con quattro uno. Nel caso non venga eseguita la prima word, ad esempio, come conseguenza di un salto condizionato, questo codice verrà interpretato come un'istruzione NOP, che non fa nulla.

Codificazione in binario dell'istruzione "addwf 004 h, 0, 1".