# PROPRIETÀ E-SINTESI

Proseguiamo il nostro percorso nell'elettronica digitale scoprendo alcune delle sue regole di base ed eseguendo la sintesi e la realizzazione di un semplice circuito logico a partire dalla sua tabella di verità.

el fascicolo 20 abbiamo presentato le porte logiche, che costituiscono le fondamenta dei circuiti logici combinatori. Abbiamo anche visto come a ognuna di esse sia associata

#### 'un'espressione matematica'.

Un circuito combinatorio, quindi, può essere rappresentato, oltre che in forma 'elettronica', anche attraverso una o più equazioni matematiche. Proprio come le espressioni matematiche, anche quelle logiche sono vincolete de una serie di regole e proprietà che permettono di interpretarle e di 'svolgere' correttamente i calcoli. Vediamo le principali, prima di dedicarci a un semplice esempio di sintesi logica.

#### PRIORITÀ DEGLI OPERATORISS

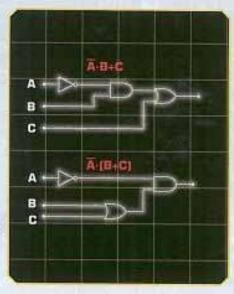

La prima regola necessaria per 'interpretare' correttamente un'espressione logica è stabilire le priorità per gli operatori (ossia stabilire in che ordine devono essere letti ed eseguiti i singoli operatori presenti). In particolare, vengono svolte prima le negazioni, poi i prodotti e per ultime le somme logiche. Per fare un esempio, consideriamo l'espressione seguente:

A B+C

Basandoci sulle regole precedenti, il suo svolgimento avviene secondo questa sequenza di operazioni:

- -negare il valore di A

- -calcolare il prodotto A-B

- -calcolare infine la somma (A-B) + C

Mel caso in cui si volessero alterare le priorità è possibile far ricorso all'uso delle parentesi. Ad esempio, se riscrivessimo l'espressione precedente in questa maniera:

A-(B+C)

la priorità di svolgimento verrebbe modificata (sarebbero eseguite prima le parentesi). La procedura di svolgimento sarebbe allora:

-negare il valore di A

-svolgere la somma (B+C)

-calcolare il prodotto A · (B+C)

Per comprendere come le due espressioni siano significativamente differenti, è possibile confrontare i due schemi elettrici equivalenti mostrati nella figura sopra, nella quale è visibile in maniera molto chiara il differente collegamento delle porte utilizzate.

#### PROPRIETA ASSOCIATIVADO

Vale sia per le somme logiche che per i prodotti e asserisce che la somma (o il prodotto) di due o più variabili non cambia se a una o più di esse si sostituisce la somma (o il prodotto) delle stesse. Ad esempio:

$$A+B+C=A+(B+C)=(A+B)+C=...$$

$A\cdot B\cdot C=A\cdot (B\cdot C)=(A\cdot B)\cdot C=...$

### PROPRIETA DISTRIBUTIVA...

Consente di 'raccogliere' una variabile (o un'espressione) logica che compare in tutti gli addendi di una somma di prodotti. Ad esempio:

#### PROPRIETÀ COMMUTATIVA

Vale sia per la somma che per il prodotto e afferma che invertendo addendi o fattori il risultato non cambia. Ad esempio:

#### PROPRIETA DI IDEMPOTENZA\*\*\*

Vale sia per la somma che per il prodotto e afferma che se si somma o si moltiplica più volte una variabile con se stessa, il risultato è uguale al valore della variabile. Ossia:

$$(A+A+A+A+...)=A$$

$$(A\cdot A\cdot A\cdot A\cdot A\cdot ...)=A$$

#### PROPRIETÀ DELLA NEGAZIONE\*\*\*

Vale la proprietà della doppia negazione, la quale afferma che se una variabile (o un'espressione) viene negata due volte, le due negazioni si annullano. Matematicamente:

#### TEOREMI DI DE MORGANIII

Sono due importanti teoremi che consentono di riscrivere somme sotto forma di prodotti e viceversa. Tali teoremi affermano che:

$$\overline{(A \cdot B \cdot C \cdot ..N)} = \overline{A} + \overline{B} + \overline{C} + ..\overline{N}$$

$\overline{(A + B + C + ..N)} = \overline{A} \cdot \overline{B} \cdot \overline{C} \cdot ..\overline{N}$

#### PROPRIETÀ DEL PRODOTTO»

Valgono le seguenti proprietà (utili per 'semplificare' circuiti ed espressioni):

#### PROPRIETA DELLA SOMMANI

Valgono le seguenti proprietà (utili per 'semplificare' circuiti ed espressioni):

$$A+O=A$$

$A+1=1$

$A+\overline{A}=1$

#### UN SEMPLICE ESEMPIO DI SINTESI »

Ora che abbiamo elencato le principali proprietà degli operatori logici, cerchiamo di capire cosa significa 'progettare' un circuito logico (di tipo combinatorio)

e in che modo è possibile

farlo. Progettare un circuito

combinatorio significa ideare

una rete logica in grado di

elaborare i dati in ingresso

secondo lo schema desiderato.

Il processo di progettazione inizia con l'individuazione delle variabili di ingresso e di uscita di cui abbiamo bisogno. Una volta identificate le variabili logiche coinvolte si procede alla compilazione di

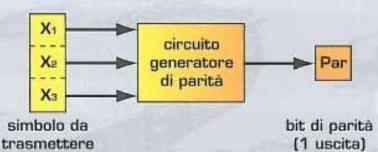

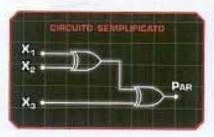

Lo schema del generatore di parità che progetteremo, con tre variabili di ingresso (X<sub>c</sub>) e una di uscita (Par).

(3 ingressi)

una tabella di verità che descrive in modo completo il comportamento della rete logica (ingressi e uscita). In ultimo si 'sintetizza' il circuito appena definito (ossia si ricava dalla tabella di verità l'espressione logica equivalenta). Per capire in modo 'interattivo' l'intero processo di progettazione, ricorriamo a un semplice esempio concreto: progettiamo un piccolo generatore di parità per simboli a 3 bit.

#### IL GENERATORE DI PARITÀ \*\*\*

La generazione dei bit di parità è una semplicissima tecnica di rivelazione degli errori utilizzata nella trasmissione digitale dei dati. Il suo funzionamento è estremamente semplice: in pratica, a ogni simbolo trasmesso (un simbolo è inteso come un 'insieme di bit'. nel nostro esempio 3) viene associato un ulteriore bit. chiamato 'bit di parità'. Esso ha la funzione di 'rendere pari' il numero di bit uguali a 1 del simbolo trasmesso. Ciò permette di poter 'contare' i bit 'alti' ('1') durante il processo di ricezione e di rilevare, in questa maniera, eventuali errori

di trasmissione (se viene ricevuto un numero dispari di '1' significa che vi è stato un errore nella trasmissione). Ricorrendo a un esempio, se viene trasmesso il simbolo '101', il bit di penta associato sarà uguale a 'O'. Al contrario, se il simbolo in trasmissione e '010', il bit di parità vale '1', poiché nella sequenza di bit emessi vi è un numero dispari di '1'. Descritto il funzionamento alla base del circuito, è necessario, come detto in precedenza, identificare le variabili: avremo tre variabili in ingresso (i tre bit del simbolo) e una in uscita (il bit di parità). Compiliamo ora la tabella di verità assegnando a 'Par' il valore '1' in tutte le combinazioni di ingresso che presentano un numero dispari di bit 'alti'. Ecco la tabella di verità corrispondente al circuito desiderato:

| Хз | Xa | Xt | Par |

|----|----|----|-----|

| D  | 0  | 0  | 0   |

| D  | D  | 1  | 1   |

| 0  | 1  | 0  | 1   |

| 0  | 1  | 1  | 0   |

| 1  | 0  | 0  | 1   |

| 1  | 0  | 1  | 0   |

| 1  | 1  | 0  | 0   |

| 1  | 1  | 1  | 1   |

|    |    |    |     |

Procediamo ora alla sintesi vera e propria del circuito. Una delle tecniche più diffuse per sintetizzere le tabelle di verità consiste nella scrittura di una somma di prodotti tra le combinazioni di ingresso che portano a '1' l'uscita. Vediemo come procedere. Iniziamo identificando tutte le righe con uscita alta [evidenziate in rosso nella tabella di verità). Il comportamento di ognuna di esse può essere replicato per mezzo di una porta logica 'AND' a 'n' entrate (nel nostro caso 3), che svolga il prodotto tra le variabili di ingresso, lasciate invariate se uguali a 1 o negate se, invece, uguali a O. La seconda riga della tabella, che ha ingressi  $X_3=0$ ,  $X_9=0$ ,  $X_1=1$ , sarà rappresentata dal prodotto:

[X<sub>3</sub> e X<sub>2</sub> sono negate in quanto uguali a 'O', mentre X<sub>1</sub> rimane invariata dato che è pari a '1']. In ugual modo, la terza riga corrisponderà al prodotto:

$$\overline{X_3}$$

$X_9$   $\overline{X_1}$   $[X_1=X_3=0, X_9=1]$

e così via per le due rimanenti righe con Par=1'. Definiti tutti i casi 'alti' è sufficiente 'sommare' (operatore 'OR') le sottoespressioni ottenute per avere il circuito logico finale. L'espressione completa del circuito sarà quindi:

$$\begin{aligned} \text{Per} &= \overline{X_3} \cdot \overline{X_2} \cdot X_1 + & & & \textbf{2" rigo} \\ &+ \overline{X_3} \cdot \overline{X_2} \cdot \overline{X_1} + & & & \textbf{3" rigo} \\ &+ X_3 \cdot \overline{X_2} \cdot \overline{X_1} + & & & \textbf{5" rigo} \\ &+ X_3 \cdot \overline{X_2} \cdot \overline{X_1} + & & & \textbf{8" rigo} \end{aligned}$$

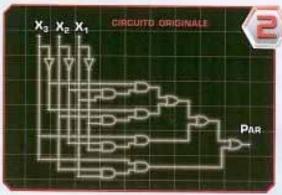

Tale espressione è equivalente al circuito logico combinatorio

mostrato qui sepre in guesta pagina. Ora dedichiamoci ad alcune brevi considerazioni. Innanzitutto si nota che nel circuito non sono state usate porte logiche 'AND' e 'OR' a più di due ingressi. Questo proprio perché normalmente le porte logiche integrate rispecchiano la natura binaria dell'operatore booleano corrispondente (sono quindi a due ingressi). Esistono comunque porte complesse (ad esempio AND a quattro ingressi), ma noi faremo riferimento alle porte a due sole entrate, che sono un buon indice della 'complessità'

del circuito progettato. Uno dei modi per 'quantificare' la complessità di una rete logica, infatti, consiste nel 'contare' fisicamente il numero di porte elementari richieste per realizzarla. Nel caso del sistema appena progettato è necessario utilizzare tre porte 'NOT', otto 'AND' e tre 'OR', per un totale di 14 porte logiche (come publi contare nello scheme). Il numero di porte logiche utilizzate è importante in quanto è direttamente legato al numero di dispositivi elettronici richiesti per realizzare il circuito. Poiché

con l'aumentare di questo numero aumentano anche costi e consumi, l'obiettivo è sempre quello di cercare di mantenere il sistema il più semplice possibile. In guesta caso, poiché in ognuno dei componenti usati nel precedente StepbyStep erano contenute sei porte 'NOT', quattro 'AND' o quattro 'OR', per poter costruire il nostro generatore di parità avremo bisogno di quattro differenti circuiti integrati (uno per le porte 'NOT', uno per le porte 'OR' e due per le 'AND'). Ma i circuiti logici possono anche essere semplificati...

## STEPDYSTEP

## UN GENERATORE DI PARITÀ

In questo StepbyStep sperimenterai il generatore di parità che abbiamo progettato all'interno dell'articolo. Prima di passare alla realizzazione 'pratica' del circuito, tuttavia, soffermiamoci sull'espressione logica ricavata e sullo schema elettronico a essa associato, mostrato nella pagina precedente.

Come abbiamo già avuto modo di osservare, l'espressione ricavata richiede per la sua implementazione fisica l'utilizzo di ben 14 porte differenti (tre porte 'NOT', otto 'AND' e tre 'OR'). Vediamo ora in che modo è possibile semplificarla. Innanzitutto richiamiamo l'espressione logica alla base del circuito:

$$Par = \overline{X_3} \cdot \overline{X_2} \cdot X_1 + \overline{X_3} \cdot X_2 \cdot \overline{X_1} + X_3 \cdot \overline{X_2} \cdot \overline{X_1} + X_3 \cdot X_2 \cdot X_1$$

Da essa puoi vedere come nei primi addendi compaia il fattore NOT X<sub>3</sub>, mentre negli ultimi due sia comune il termine X<sub>3</sub>. Raccogliamo questi due termini sfruttando la proprietà distributiva. L'equazione diventa:

$$Per = \overline{X_3} \cdot \left( \overline{X_2} \cdot X_1 + X_2 \cdot \overline{X_1} \right) + X_3 \cdot \left( \overline{X_2} \cdot \overline{X_1} + X_2 \cdot X_1 \right)$$

Ora osserva il contenuto delle parentesi. La prima delle due è un'espressione equivalente alla scrittura:

Ā-B+ Δ-Ē

| Α | В | Υ.  |

|---|---|-----|

| 0 | D | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 110 |

| 1 | 1 | .0  |

La tabella di verità associata a tale espressione è mostrata qui sopra e, come puoi osservare, è identica a quella operatore logico XDR, presentata nel fascicolo 20. Possiamo quindi sostituire l'intera sottoespressione con l'espressione equivalente X<sub>2</sub> XOR X<sub>1</sub>. Alla stessa maniera osserva il secondo blocco: anch'esso ha un comportamento già noto. Assume, infatti, valore di uscita alto solo quando le variabili X<sub>1</sub> e X<sub>2</sub> sono uguali: in pratica è un'espressione equivalente all'operatore logico XNOR. Possiamo sostituire anch'esso con la corrispondente forma semplificata. La rete logica diviene quindi:

Par=

$$\widetilde{X}_3 \cdot (X_9 \oplus X_1) + X_3 \cdot (X_9 \oplus X_1)$$

Ora soffermati ancora sull'attuale struttura dell'espressione logica: puoi osservare nuovamente una forma del tipo  $\overline{A} \cdot B + A \cdot \overline{B}$  (con  $B = (X_2 \text{ XOR } X_1)$  e  $A = X_3$ ). Come abbiamo fatto in precedenza possiamo semplificare l'attuale espressione per mezzo dell'operatore logico XOR. La rete logica diviene allora:

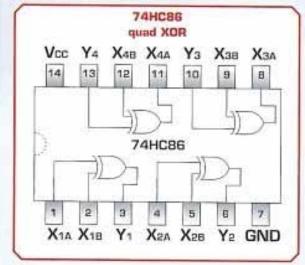

$$Par= X_3 \oplus (X_2 \oplus X_1)$$

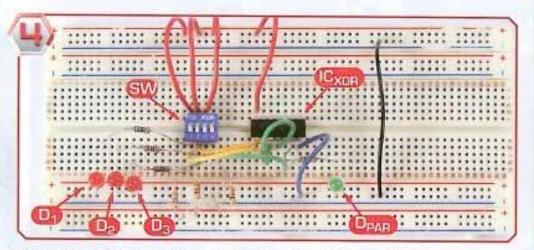

Abbiamo ridotto il circuito iniziale, composto da ben 14 porte logiche, a un circuito equivalente formato da due sole porte elementari. Con un po' di pratica, è possibile applicare le proprietà degli operatori logici per ridurre fortemente la complessità dei circuiti logici progettati. Proveremo a questo punto a realizzare il circuito semplificato e a verificare la sua equivalenza con quello originale. Le porte XOR che userai sono contenute nell'integrato 74HC86.

Ecco il materiale necessario per questo esperimento:

- (1) una breadboard

- 42) fili per breadboard

- 43) un 74HC86 (ICxon)

- (4) un microswitch a 4 vie (SW)

- (5) tre LED rossi (D, D, D, D)

- (6) tre resistori da 4,7 kohm (R<sub>ii</sub>)

- (7) un LED verde (DPAR)

- (8) quattro resistori da 220 ohm (R<sub>0</sub>)

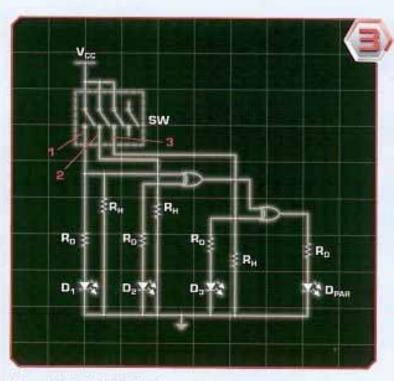

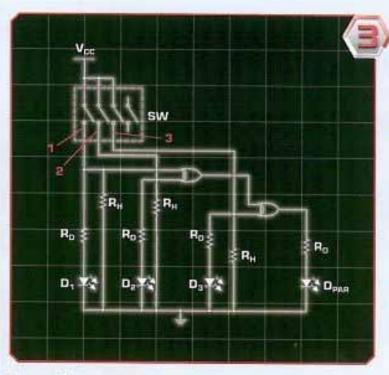

In questo StepbyStep realizzerai Il circuito generatore di parità che abbiamo progettato e 'semplificato' nelle precedenti pagine. Come hai potuto vedere, infatti, applicando opportunamente le proprietà dell'algebra booleana e l'equivalenza delle espressioni logiche, siamo riusciti a ridurre il circuito originale, composto da ben 14 porte logiche (figura a lato), ricavandone uno equivalente formato da porte XOR (figura sotto). Tali porte elementari sono contenute all'interno del circuito integrato 74HC86 (della stessa sottofamiglia di quelli usati nel precedente Workshop), la cui struttura interna è mostrata nello schema a sinistra. Come tutti gli integrati logici, anche questo dovrà essere alimentato attraverso i pin 14 e 7.

A lato puoi vedere mostrato il circuito che dovrai realizzare. Come al solito andrà alimentato per mezzo di un portapile da quattro pile 'stilo'. i cui fili saranno associati al terminale V<sub>cc</sub> e alla massa del circuito. Ricordati che a tali terminali dovranno essere collegati anche i pin 14 (V<sub>cc</sub>) e 7 (GND) del circuito integrato 74HC86, I primi tre interruttori del microswitch (SW) ti consentiranno di impostare il valore delle tre linee di ingresso al circuito.

Portandoli su 'ON', infatti, ti sarà possibile collegare gli ingressi a V<sub>CC</sub>, e quindi al valore logico '1'. Aprendoli, invece, (ossia portandoli su 'OFF'), i pin di ingresso delle porte logiche saranno collegati a massa attraverso i resistori R<sub>H</sub>. R<sub>H</sub> svolge un ruolo importante, in quanto evita il verificarsi di cortocircuiti nel momento in cui vengono chiusi gli interruttori di SW (di fatto limita il flusso di corrente tra V<sub>CC</sub> e massa).

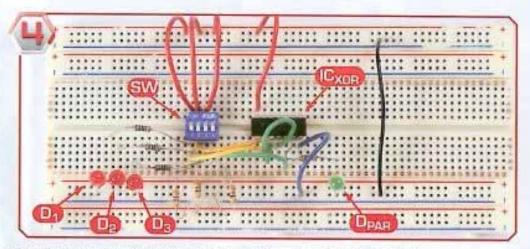

In figura puoi vedere il circuito montato su breadboard. I tre LED in basso a sinistra, indicati con D<sub>1</sub>, D<sub>2</sub> e D<sub>3</sub> sono i tre dispositivi luminosi che ti permettono di visualizzare lo stato delle linee di ingresso. Si accenderanno in presenza di ingressi alti (interruttori su ON) e si spegneranno in caso di ingressi bassi. Un comportamento analogo vale per il LED D<sub>PAR</sub>, che ti mostrerà il valore del bit di parità generato dal circuito logico che abbiamo progettato. Se avrai montato correttamente il circuito, dopo averlo alimentato scoprirai che indipendentemente dallo stato degli interruttori del microswitch (e quindi delle variabili logiche di ingresso) il numero totale dei LED accesi sarà sempre pari (ossia O, 2 o 4). Se vuoi, per fare pratica, puoi riprogettare il circuito in modo da farlo funzionare con quattro linee di ingresso (la tabella di verità sarà composta, quindi, da 24=16 righe).

A lato puoi vedere mostrato il circuito che dovrai realizzare. Come al solito andrà alimentato per mezzo di un portapile da quattro pile 'stilo', i cui fili saranno associati al terminale V<sub>cc</sub> e alla massa del circuito. Ricordati che a tali terminali dovranno essere collegati anche i pin 14 (Vcc) e 7 (GND) del circuito integrato 74HC86. I primi tre interruttori del microswitch (SW) ti consentiranno di impostare il valore delle tre linee di ingresso al circuito.

Portandoli su 'ON', infatti, ti sarà possibile collegare gli ingressi a V<sub>CC</sub>, e quindi al valore logico '1'. Aprendoli, invece, (ossia portandoli su 'OFF'), i pin di ingresso delle porte logiche saranno collegati a massa attraverso i resistori R<sub>H</sub>. R<sub>H</sub> svolge un ruolo importante, in quanto evita il verificarsi di cortocircuiti nel momento in cui vengono chiusi gli interruttori di SW (di fatto limita il flusso di corrente tra V<sub>CC</sub> e massa).

In figura puoi vedere il circuito montato su breadboard. I tre LED in basso a sinistra, indicati con D<sub>1</sub>, D<sub>2</sub> e D<sub>3</sub> sono i tre dispositivi luminosi che ti permettono di visualizzare lo stato delle linee di ingresso. Si accenderanno in presenza di ingressi alti (interruttori su ON) e si spegneranno in caso di ingressi bassi. Un comportamento analogo vale per il LED D<sub>PAR</sub>, che ti mostrerà il valore del bit di parità generato dal circuito logico che abbiamo progettato. Se avrai montato correttamente il circuito, dopo averlo alimentato scoprirai che indipendentemente dallo stato degli interruttori del microswitch (e quindi delle variabili logiche di ingresso) il numero totale dei LED accesi sarà sempre pari (ossia O, 2 o 4). Se vuoi, per fare pratica, puoi riprogettare il circuito in modo da farlo funzionare con quattro linee di ingresso (la tabella di verità sarà composta, quindi, da 24=16 righe).